CPU vs GPU vs FPGA vs ASIC

Flexibility < ——> Efficiency

1. DSP: digital signal processors (TI, Freescale/NXP, ADI)

GitHub – mikeroyal/DSP-Guide: Digital Signal Processing(DSP) Guide

Introduction — PySDR: A Guide to SDR and DSP using Python

B4860-Baseband-Processor

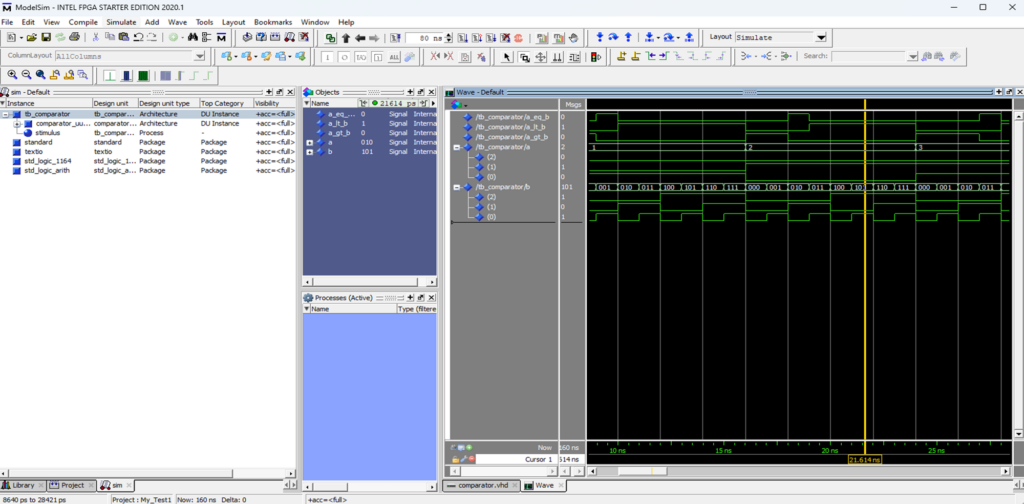

2. ModelSim RTL (VHDL, Verilog)

Reference source code: VHDL coding tips and tricks (vhdlguru.blogspot.com)

Download: www.intel.com › content › wwwModelSim-Intel®

Running VHDL Simulation with ModelSim

write your VHDL_code.vhd

write the test_bench.vhd

compile –> simulation

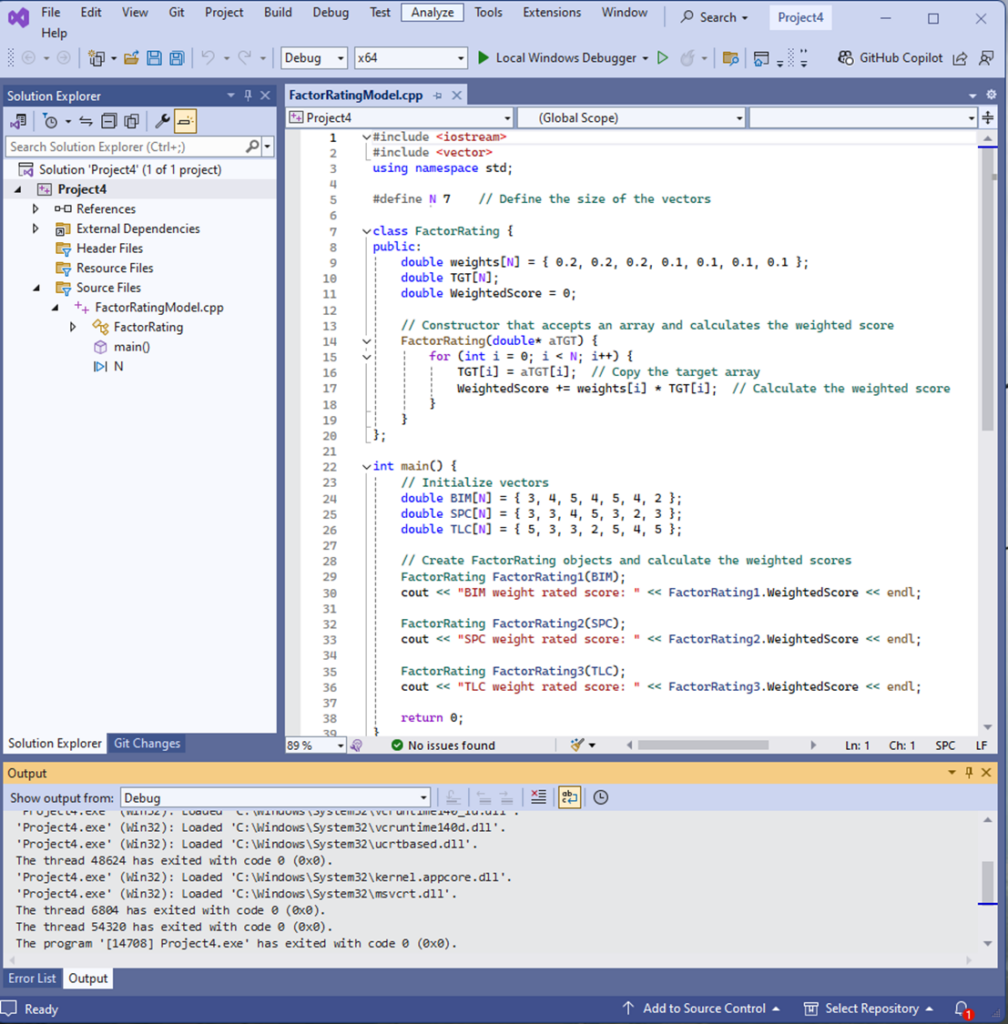

3. Programming Language C++ : cplusplus.com/doc/tutorial/

C/C++ tool installation, edit, compile and run

1) Download the MS Visual Studio from: https://visualstudio.microsoft.com/downloads/

Or, Download MS Visual Studio from: https://visualstudio.microsoft.com/vs/older-downloads

(Download Visual Studio Tools – Install Free for Windows, Mac, Linux (microsoft.com) )

2) Or, Download the Code Blocks from: https://www.codeblocks.org

3) Learning C/C++ in Visual Studio: https://learn.microsoft.com/en-us/cpp/overview/visual-cpp-in-visual-studio?view=msvc-170

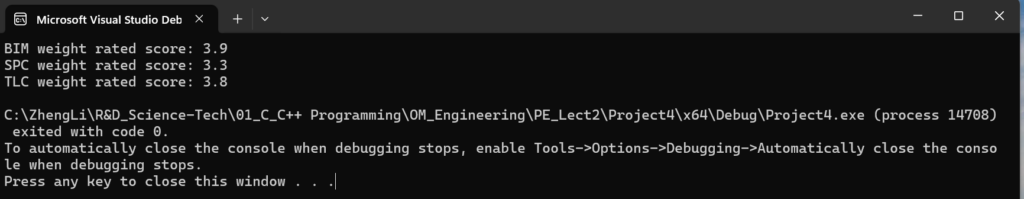

Coding example: The Factor-Weighted-Rating Model by C++

4. SystemC: System Level Design and Verification

systemC.org

http://www.ocpip.org

Learn SystemC – Introduction

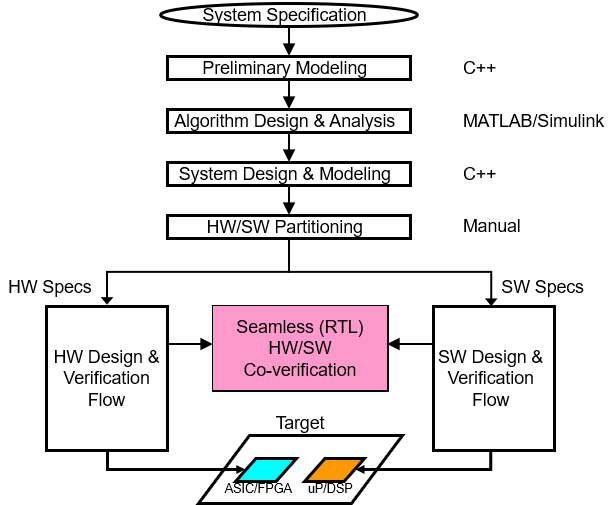

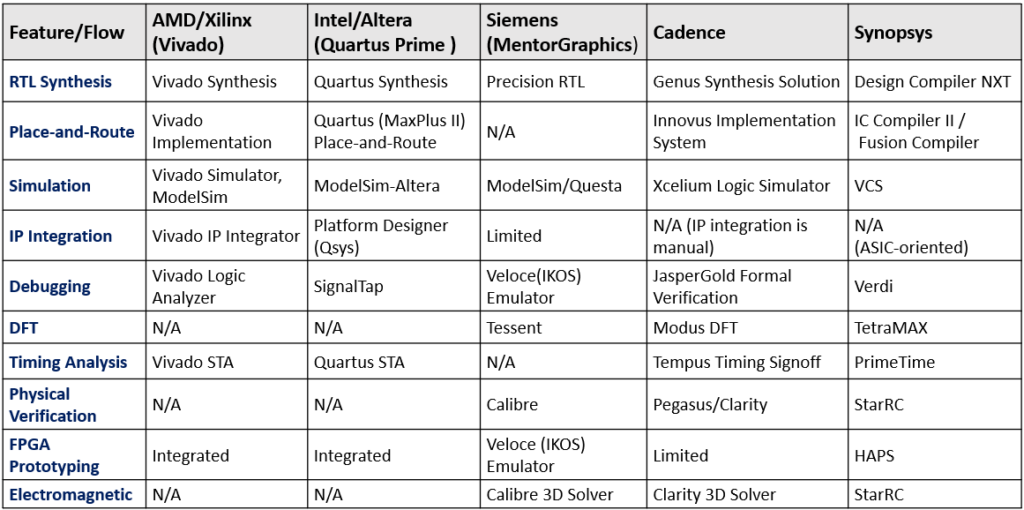

5. ASIC and FPGA design, simulation and verification Suites

1). Vivado and Quartus are specialized for FPGA workflows, tightly coupled with their respective hardware.

2). Cadence and Synopsys dominate ASIC/SoC design but offer limited FPGA workflows, with Synopsys’ HAPS and Siemens’ Veloce filling the FPGA-based emulation niche.

3). Siemens (Mentor Graphics) uniquely bridges both ASIC and FPGA workflows, providing tools for synthesis, debugging, and emulation.